先进的电源管理平台-打破效能新记录

先进的电源管理平台-打破效能新记录

一)配置1:

在第一种配置中,电源管理能力降至最低。芯片使用外部PMIC以Go-No-Go方式产生电源电压。不使用休眠模式,芯片只是处于运行或断电状态(参见图11)。

从SoC设计的角度来看,这种配置是最简单的,结果是PCB上较高的BOM成本,而且没有权利管理电源。

因此,这种配置被认为是功耗方面最差的情况,被视为 是ULPMark-CP的参考分数,如图17所述。

Fig. 11: Configuration 1

ii)配置2:

在第二种配置中,大多数与电源管理相关的解决方案都已在芯片中实现,但设计时间较长。这种方法需要专业的工程师来管理所有不同的技术和IP以及UPF( Unified Power Format)。

这种方法的主要目的是使休眠模式与电源和时钟门控技术结合起来,最大限度地减少功耗,特别是对于ULP MCU执行的低占空比操作。

数字域的电源门控实现了深度休眠模式。在这种模式下,只有一部分芯片保持运行,以保留一些数据或启用唤醒,即所谓的Always-On域。该域通常由高Vt或厚氧化物标准单元组成,因为其低漏电值通常为0.8 V或0.9 V,具体取决于工艺技术。与配置1相比,这种策略可使ULPMark-CP得分提高62倍(参见图17)。

为了实现这一改进,必须永久运行一些软件,作为MCU的PMU。即使它可以在非常低的功率模式下运行(例如在1 MHz下),甚至在睡眠模式下也仍然会消耗功率,从而将增益降低了4倍(参见图17)。

最后,在集成稳压器上运行可带来额外的能效提升,转化为10%的提高。

总体而言,ULPMark-CP得分提高了16倍,这是一个巨大的进步,这说明了为什么越来越多的公司现集成了稳压器和电源管理模块。

图12:配置2

三)配置3。

虽然前一种方法有很大的收益,但它会因软件模拟单片机的PMU而产生功耗。

为此,最先进的公司已经用轻量级的有限状态机(FSM)PMU取代了SW PMU。这种方法大大降低了功率损失,在ULPMark-CP得分提高了3倍(参见图13)。

然而,由于这些MCU将在大量的应用场景下使用,FSM的缺乏或有限的可重构性可能是一个问题。

Fig. 13: Configuration 3

四)配置4:

在FSM上的超低功耗PMU操作与SW PMU的高可重构性之间存在一种折衷的解决方案。

Dolphin Design的嵌入式电源控制器MAESTRO是一种完全可配置的软件IP,可控制SoC电源管理,从启动到最先进的DVFS方案以及时钟和电源门控方案。该IP不仅具有与有限状态机相关的优势(超低功耗和预编程模式),还可以通过其驱动程序在现场进行重新编程,并提供与MCU上PMU软件相同的可配置性。

MAESTRO拥有一套全面的稳压器,在运行模式下,它能有效地转换输入的电池电压。所有这些IP都是可配置的,以满足确切的需求并建立一个最佳的电源网络,同时控制BOM和集成成本。这些IP可以优化运行模式下的功耗。

深度休眠模式下的漏电是ULP MCU的主要耗电因素,因此我们开发了一套独特的Always-On解决方案,以实现超低漏电。这套IP不仅包括超低静态LDO,还包括专用振荡器和电源门控解决方案。

这种基于FSM的可配置方法避免了唤醒MCU。

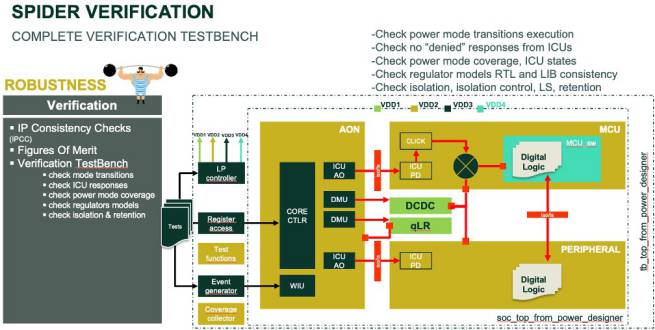

软件IP可以很容易地用PowerStudio进行配置,PowerStudio是一个专门的配置平台(参见图14),它在配置PMU的同时可以构建优化的电源网络(参见图14)。第二步,配置好的RTL会自动生成相关的验证测试平台和相关的IP一致性检查,以实现稳健的集成(参见图15)。

Fig. 14: Dolphin Design PowerStudio GUI

Fig. 15 : Dolphin Design PowerStudio verification and IP consistency checks

除了PowerStudio,Dolphin Design的SPIDER还提供了一系列的超低漏电IP,通过降低休眠模式下的漏电来进一步提升性能。

Dolphin Design名为CLICK的解决方案取代了标准的PMK,这是一个可调的电源门控解决方案,提供了2.2倍的性能提升。这种提升主要来自于以下事实,即由于Ron/Roff比率可在线调整,因此必须集成较少数量的开关,从而限制了睡眠模式下的额外漏电。

Fig. 16: Dolphin Design IP offering to enable active power management

另一个改进来自于用Dolphin Design独特的AON标准单元取代传统的HVT标准单元,这种单元虽然在相同的电压下工作,但漏电率更低。这提供了1.5倍的额外性能提升。

最后,使用超低漏电线性稳压器为Always-On域供电,由于静态电流的增益,带来了1.1倍的性能提升(参见图16)。

总体而言,与配置3相比,SPIDER的ULPMark-CP得分提高了3.6倍,这是最有效的电源管理策略。与被动管理电源的情况相比,增加到135倍的巨大提升(参见图17)。

5)成果总结与标杆

在本文中,我们探讨了各种通用配置如何逐步提高MCU的功率指标。探讨的两个主要参数是休眠模式下的漏电流(单位:μA)和运行模式下的能效(单位:μA/MHz)。这些参数是ULPMark-CoreProfile (CP)分数的核心,该分数被广泛用于微控制器的基准测试。与MCU微架构密切相关的ULPMark-Peripheral Profile (PP)相比,ULPMark-CP几乎完全与电源管理策略相关,因为现在大多数MCU使用相同的CPU(通常是Cortex-M4或Cortex-M7)。

a)结果总结

ULPMark-CP得分的改进(相对于配置1)总结如下。第一条分数线是指从配置N-1到配置N的相对改进(例如,在配置3和4之间观察到3.6倍的改进)。第二条分数线指的是自配置1开始的绝对改进(例如,在配置1和4之间观察到135倍的改进)。

Fig. 17: ULP MCU configurations ULPMark scores comparison

使用Dolphin Design的SPIDER所获得的最高分数来自该平台中同类最佳的IP。该平台还提供其他好处:它的建立是为了在IP之间提供强大的一致性,并实现简单而强大的实现,从而通过经过优化和经过硅验证的IP集来实现最高效的电源网络。

b)SPIDER平台概述

图18对这种方法进行了全局解释。为了方便电源架构工程师,SPIDER平台嵌入了一个名为PowerStudio的GUI,它有助于在规范阶段定义、架构和构建任何类型的电源网络。自动计算出功绩值(FOM),并可使用FOM Podium功能进行比较,以确保产品的最佳选择。在此阶段,不仅要根据应用目标选择稳压器和电源门控解决方案并确定其大小,而且还要对MAESTRO电源控制器进行全面配置(包括启动序列和所有预编程的过渡序列)。

一旦选择完成,由于在第一阶段执行的配置计划是一个更大的域的一部分,因此该PMU RTL会自动生成,而IP已得到充分验证。

在第三阶段,适当的IP兼容性检查与自动生成的验证测试台一起运行,以检查RTL中的PMU集成。

最后,在运行时,MAESTRO可以通过软件(提供驱动程序)按需重新配置。如果不需要它,它就像标准的FSM一样在预编程的启动序列和过渡序列上运行。

图18:SPIDER平台一瞥

c)行业标杆

由于与最先进的产品配置相比,其3.6倍的得分看起来过于乐观,因此我们已经在硅片上运行了一些MCU(采用40 nm LP和22FDX技术),以测量休眠模式下的泄漏电流和运行模式下的能效。实验结果如图19所示。40LP试验着重于芯片布局的公开,因为当今大多数商用MCU使用的技术范围从90 nm到40 nm。

大多数知名的MCU公司都在其网站或应用说明中提供了其商用芯片的类似测量结果。图19总结了大范围的MCU的一些值,包括ULP MCU(最大频率为100MHz)和高性能MCU(最大频率等于或大于200MHz)。

从这个基准来看,很明显,即使我们正在比较相同的技术节点(40 nm)和等效的内核(Cortex-M4或M7或等效的内核),Dolphin Design的SPIDER仍可以实现超过3倍的得分,如图17所示。

Fig. 19: SPIDER ower Management Platform gains

6) 结论

利用其SPIDER平台,Dolphin Design提供了一个交钥匙的解决方案,以加快先进电源管理解决方案的设计,从架构到实施,并在几周内而不是几个月内达到最终的能效数字。

Dolphin Design带来了最先进的解决方案,其结合了最先进的电源管理IP组合(低漏电LDO、微功率高效DC-DC)、可扩展至任何SoC复杂度的全配置低功耗电源控制器IP,以及独特的PowerStudio系统工具,加快了电源架构探索和PMU无缝集成的速度,从而保证了芯片的安全性,并使上市时间处于可控状态。

专注于您的核心竞争力,用更少的能源做更多的事。

关于作者

2018年,苏希尔·姆希拉获得了艾克斯-马赛大学的电气工程博士学位,她致力于先进的现场监控,为汽车和任务关键型应用提供超低功耗集成电路和高度可靠的微控制器。她的工作涵盖了从设计规格到产品工程的所有方面。之后,她加入了曼托图形公司,担任应用工程师

皮埃尔·加泽尔于2006年毕业于巴黎高等电子技术学院,获得电子工程硕士学位。2015年,他获得格勒诺布尔管理学院技术与创新管理行政硕士学位。皮埃尔负责海豚设计公司蜘蛛平台的业务开发和产品营销。在加入海豚之前,他在意法半导体工作了12年,先后在数字设计流程和方法领域担任R&D工程师、高级工程师和高级技术主管。在此期间,皮埃尔致力于为成熟和先进的硅技术节点开发数字设计平台,并参与了针对物联网、汽车、图像传感器和微控制器市场的关键片上系统和专用集成电路项目。

关于海豚设计

海豚设计公司(Dolphin Design)总部位于法国,前身为海豚集成公司(Dolphin Integration),是一家半导体公司,拥有160名员工,包括140名高素质工程师。

它们提供基于最先进的入侵防御系统和体系结构的差异化平台解决方案,由独特的系统级实用程序定制,以提供由客户或为客户设计的快速、安全的专用集成电路。这些平台可用于各种工艺流程,并针对高能效片上系统设计进行了优化。

他们的客户现在已经超过500家,他们专注于人类、创新和长期合作,使他们能够将产品和设备带到数十亿人的手中,这些产品和设备由创新和可访问的集成电路驱动,将环境影响降至最低。在包括物联网、人工智能和5G在内的消费市场,以及高可靠性市场,它们释放了SoC设计师的创造力,带来了差异化。

告诉他们你最大的梦想。挑战不可能。他们启动了它。

参考

https://www.eembc.org/ulpmark/

https://blogs.mentor.com/verificationhorizons/blog/2019/03/05/part-11-the-2018-wilson-research-group-functional-verification-study/