使用Questa®VIP进行ArasanMIPI®CSI-2-RX IP验证

本文介绍了由西门子业务部Mentor使用Questa®VIP进行的ARASANMIPI®CSI-2-RX IP核的验证过程。

MIPI CSI-2协议

MIPI摄像机串行接口2(CSI-2)在外围设备(例如摄像机模块)和主机处理器(例如基带或应用程序引擎)之间提供接口。 它主要用于移动和汽车行业。 高性能和低功耗是该协议的关键功能。

MIPI CSI-2提供了两个高速串行数据传输接口选项。 第一个选项称为D-PHY物理层选项,它使用具有一个2线时钟通道和一个或多个2线数据通道的差分接口。 第二个高速数据传输接口选项(称为C-PHY物理层选项)使用一个或多个单向3线串行数据通道,每个通道都有其自己的嵌入式时钟。

ARASAN MIPI CSI-2接收器IP

Arasan MIPI CSI-2接收器IP提供了一个标准的,可扩展的,低功耗和高速接口,该接口支持各种高分辨率的图像。它符合MIPI CSI-2 v1.3规范,并支持D-PHY v1.2和MIPI C-PHY v1.1。

Arasan提供了一种组合配置的C-PHY,该配置同时支持C-PHY接口和D-PHY接口。该IP通过符合D-PHY和C-PHY规范的PHY协议接口(PPI)接口连接到D-PHY或C-PHY。除每种模式中的一些其他信号外,大多数PPI信号对于D-PHY和C-PHY是通用的。通过基于用例的简单编程来选择PHY的用法。

Arasan CSI-2 Rx IP,CSI-2 Tx IP,D-PHY IP和C-PHY IP经过硅验证,目前用于MIPI协议分析仪和生产测试应用中。 MentorQuesta®VIP进一步提高了Arasan IP对MIPI规范的合规性,使IP能够满足合规性测试应用程序的严格要求。

以下是Arasan MIPI CSI-2接收器IP的主要功能:

-通过用户配置使用D-PHY或C-PHY

-4层或8层D-PHY和3层C-PHY

-支持超低功耗模式(ULPS)

-在C-PHY模式下支持备用低功耗状态(ALPS)

-ISP的单(或)可选多像素模式接口

-多像素模式用于高带宽要求的应用中,以降低ISP时钟频率要求。

-具有HSYNC,VSYNC,DATA和DATA VALID的ISP的可选像素级接口

-根据ISP的通道配置将接收到的像素流传输到八个数据通道(可自定义)

-短通用数据包的单独数据通道

-支持所有数据包级别错误,协议解码级别错误

支持的像素格式:

-RAW数据类型– RAW6,RAW7,RAW8,RAW10,RAW12,RAW14,RAW16,RAW20

-YUV数据类型– YUV422-8位,YUV422-10位,旧版YUV420 8位,YUV420 10位,YUV420 8位(色移像素采样),YUV420 10位(色移像素采样)

-RGB数据类型– RGB888,RGB666,RGB565,RGB555,RGB444

-所有用户定义的数据类型/ JPEG

-通用的8位长数据包数据类型

-对CSI-2和PHY相关寄存器进行编程的能力PHY相关寄存器的保留地址空间[0x00-0x0F]

主机接口,用于寄存器配置和监视

-对AHB或APB接口的可选支持

系统架构

有两种互斥的操作模式(寄存器可配置),模式0(D-PHY)和模式1(C-PHY)。 两种模式都使用公共PPI接口信号和每种模式独有的一些其他信号,如图1所示。

功能块

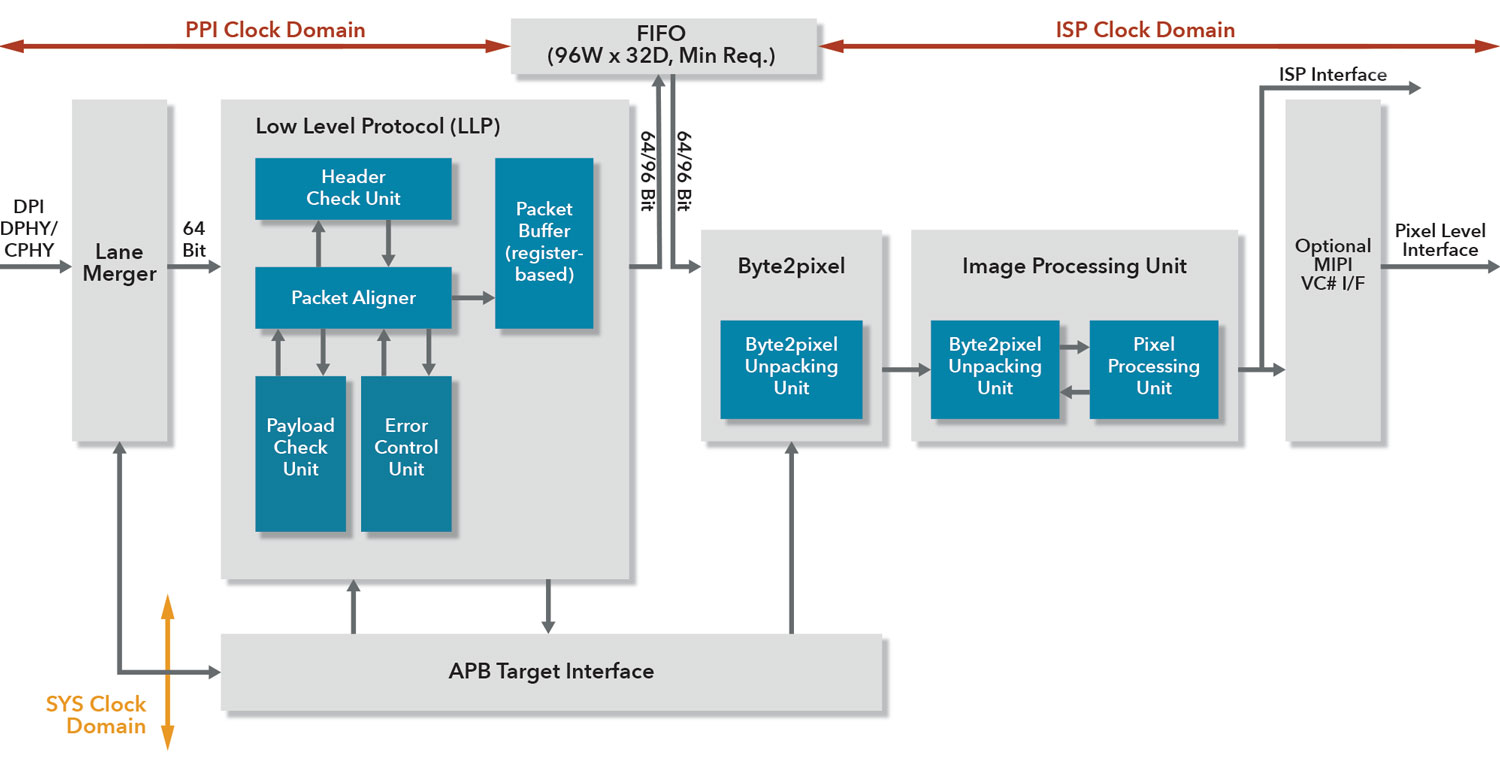

CSI-2接收器IP被划分为多个子模块,以实现以下单元所需的功能,如图2所示:

-APB目标接口

-车道合并层单元

-低层协议单位

-FIFO(外部)

-字节到像素单位

-图像处理器接口单元

-MIPI接口

CSI-2 QUESTA验证IP

CSI-2Questa®验证IP(CSI-2 QVIP)是使用高级方法构建的综合验证IP,具有先进的调试,覆盖和协议检查功能,以最快的速度完成验证。以下是CSI-2 QVIP的主要功能:

-完全符合UVM标准

-与所有流行的行业模拟器兼容

-未加密的测试序列库

-验证计划和范围

CSI-2 QVIP包含一个UVM代理,该代理已配置有活动的从属PPI外设摄像机设置。该UVM代理同时具有驱动程序和监视程序,它们分别驱动和监视从属PPI接口,如图3所示。

CSI-2 QVIP驱动程序

-通过PPI接口驱动计划的序列项

CSI-2 QVIP监视器

-从PPI接口收集CSI-2数据包

-使用断言监视协议合规性检查

-将数据包发送到记分板以进行检查

-样本覆盖率衡量验证目标的百分比

CSI-2 QVIP记分牌

-预测具有已配置设置的数据包

-将UVM_ERROR标记为预测和观察到的数据包之间的任何不匹配

使用MIPI CSI-2 QVIP进行验证

testbench验证环境是使用SystemVerilog语言开发的,并且与UVM-1.2保持一致。测试平台环境中使用的CSI-2 QVIP由西门子业务部门Mentor开发。一些测试平台组件是CSI-2 QVIP软件包的一部分,而所有其他组件都是从头开发的。

-CSI-2 IP像素接口-SystemVerilog虚拟接口,用于访问CSI-2 IP像素级接口信号

-CSI-2 IP监视器-UVM监视器将信号级别的活动转换为TLM事务,并广播来自CSI-2 IP像素接口的数据包

-CSI-2记分板-比较来自CSI-2 IP监视器和CSI-2 QVIP监视器的数据包

上面的UVM测试台从DUT调出和配置开始,这是使用APB和AHB序列完成的。配置阶段完成后,测试将开始摄像头序列,以从CSI-2 QVIP生成各种帧。

所使用的序列基于约束驱动的激励生成,这使用户可以自动生成必要的激励以进行功能验证。随机测试可能比传统的定向测试方法更有效,因为它可以生成原本会被遗漏的极端情况。它代表了一种有效的方法,可以通过很少的测试来快速实现覆盖率目标。

CSI-2 QVIP定序器从CSI-2 QVIP序列中获取序列项,并将其传递给其驱动程序,驱动程序将其转换为CSI-2 PPI接口。 CSI-2 QVIP内置监视器收集所有数据包并将其发送到记分板。 CSI-2 QVIP监视器还提供协议声明,以验证PPI接口上的DUT行为。记分板类包含两个分析FIFO和两个分析导出。其中一个连接到CSI-2 QVIP监视器,另一个连接到CSI-2 IP监视器。所有受监视的CSI-2数据包都存储在记分板FIFO中并进行比较。

结论

MIPI CSI-2Questa®验证IP高度可配置,旨在通过高级验证方法简化易用性。该VIP中使用了具有统一通用架构的大型标准SystemVerilog UVM组件库。它包括测试计划,一致性测试,测试序列,SystemVerilog和XML源代码中的协议覆盖范围,全面的协议检查,错误注入和调试功能。这些功能可确保在验证团队中快速部署,并易于重用,扩展和调试功能。

Questa®Verification IP以其灵活的体系结构提供支持,无缝集成到高级验证环境中,包括使用UVM,Verilog,VHDL和System-C构建的测试平台。它是业界唯一具有跨所有协议的本机SystemVerilog UVM架构的VIP,可确保最大的生产力和灵活性。此外,VIP解决方案的全面协议声明使Questa®Formal用户可以详尽地证明设计的正确性。

MentorQuesta®验证IP是Enterprise Verification Platform™(EVP)的组成部分。与Questa®验证解决方案一起,VIP组件减少了启动时间并实现了快速覆盖。